# TC521000P/J

1MBit (256K x 4) Field Memory

#### DESCRIPTION

The TC521000P/J is a CMOS 1Mbit Field Memory organized as 256K word by 4 bits, and features separate inputs/outputs equipped with each 8 bit serial shift register (32K words × 8 bit shift register × 4 bits), and also features a high speed operation with a clock rate of 33MHz (serial cycle time: 30ns). The TC521000P/J is a high speed serial read/write memory with a random access capability per 8 words, and is suitable for use in field/frame memory in digital TV, VCR and other video application systems which requires the improvement in picture quality and enhancement of performance.

The TC521000P/J is fabricated using TOSHIBA's CMOS silicon gate process technology as well as advanced circuitry to provide low power dissipation and wide operating margins.

#### FEATURES

· High speed and low power

| Serial Access Time | 2               | 20ns  |

|--------------------|-----------------|-------|

| Serial Read Cycle  | Time            | 30ns  |

| Serial Write Cycle | 30ns            |       |

| Read, Write Cycle  | 190ns           |       |

| Read-Modiry-Write  | 240ns           |       |

| Read-Read-Write Cy | cle Time        | 480ns |

| D Dissississis     | Operating Power | 550mW |

| Power Dissipation  | Standby Power   | 110mW |

- Organization: 32K word × 8 bit shift register × 4 bit

- Single 5V power supply: 5V±10%

- · On-chip 8 bit shift registers

- · Separate inputs and outputs

- Serial read/write, Read/Write, Read-Modify-Write, High Speed Read-Read-Write capability

- · Random Access Capability per 8 word

- 8ms/512 refresh cycles

- · On-chip refresh counter

- · All inputs and outputs: TTL compatible

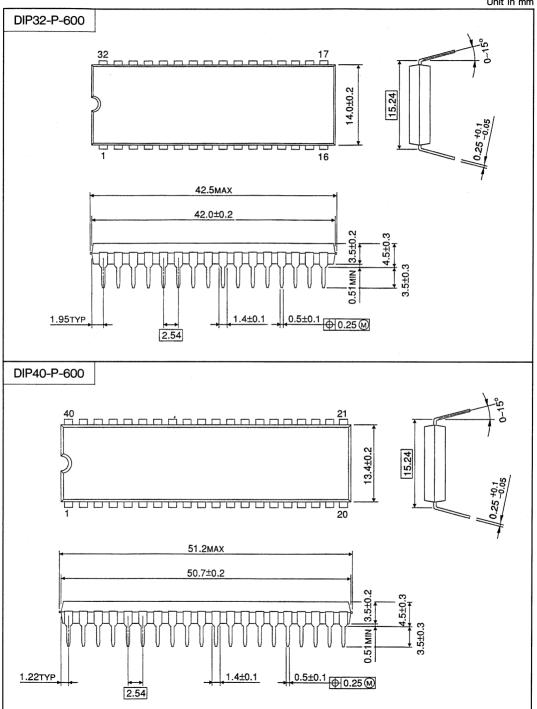

- · Package: TC521000P: DIP40-P-600

TC521000J: SOJ40-P-400

PIN CONNECTION (TOP VIEW)

| 211 001111120        | 11011 (101 111     | J. ,                 |                         |

|----------------------|--------------------|----------------------|-------------------------|

| Plast                | ic DIP             | Plast                | ic SOJ                  |

| v <sub>ss</sub> d    | 40 V <sub>CC</sub> | Vss 🗖                | 40 V <sub>CC</sub>      |

| A7 🗖 2               | 39 A 8             | A7 🗖 2               | 39 A 8                  |

| A6 🗖 3               | 38 <b>口</b> A9     | A6 <b>□</b> 3        | 38 <b>口</b> A 9         |

| A5 🗖 4               | 37 A 10            | A 5 🗖 4              | 37 🗖 ∧ 10               |

| л4 🗖 5               | 36 🗖 A 1 1         | A4 🗖 5               | 36 🗖 A I I              |

| A3 🗖 6               | 35 A 12            | A3 🗖 6               | 35 🗖 ∧ 1 2              |

| A2 🗖 7               | 34 🗖 A 1 3         | A2 🗖 7               | 34 🗖 A 13               |

| A1 🗖 8               | 33 A 1 4           | л1 🗖 8               | 33 <b>□</b> <u>∧1</u> 4 |

| A0 🗖 9               | 32 🗖 CE            | A0 <b>□</b> 9        | 32 <b>□</b> ĈĒ          |

| CS 🗖 10              | 31 RFSH            | CS 🗖 10              | 31 RFSH                 |

| NC 🗖 11              | 30 🗖 NC            | NC 🗖 11              | 30 <b>□</b> NC          |

| NC 🗖 12              | 29 <b>口</b> NC     | NC 🗖 12              | 29 NC                   |

| WE 🗖 13              | 28 <b>口</b> SF     | WE □ 13              | 28 <b>⊐</b> SF          |

| WS 🗖 14              | 27 🗖 RS            | ₩S 🗖 14              | 27 🗖 RS                 |

| DI 1 🗖 15            | 26 DI 4            | DI 1 🗖 15            | 26 🗖 DI 4               |

| DI 2 🗖 16            | 25 D I 3           | DI 2 🗖 16            | 25 DI 3                 |

| SIC 🗖 17             | 24 🗖 SOC           | SIC 🗖 17             | 24 <b>⊐</b> SOC         |

| DO1 5 18             | 23 DO4             | DO 1 🗖 18            | 23 D04                  |

| DO2 🗖 19             | 22 DO3             | DO2 🗖 19             | 22 <b>D</b> DO 3        |

| V <sub>SS</sub> □ 20 | 21 OE              | V <sub>SS</sub> □(20 | 21 OE                   |

|                      |                    |                      |                         |

PIN NAMES

| 1111 1011125 |                           |

|--------------|---------------------------|

| SYMBOL       | NAME                      |

| A0 ∿ A14     | Address Input             |

| ĈĒ           | Chip Enable Input         |

| ŌĒ           | Output Enable Input       |

| WE           | Write Enable Input        |

| WS           | Write Strobe Input        |

| RS           | Read Strobe Input         |

| CS           | Chip Select Input         |

| SIC          | Serial Input Clock Input  |

| SOC          | Serial Output Clock Input |

| DI1 ∿ DI4    | Data Input                |

| DO1 ∿ DO4    | Data Output               |

| RFSH         | Refresh Control Input     |

| SF           | Special Function Input    |

| VCC          | Power (5V)                |

| $v_{SS}$     | Cround                    |

| NC           | Non Connection            |

#### PIN NAMES AND FUNCTIONS

| SYMBOL    | NAME                         | FUNCTION                                                                                                                                                                     |

|-----------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A0 ∿ A8   | Row Address Inputs           | Row Addresses                                                                                                                                                                |

| A9 ∿ A14  | Column Address Inputs        | Column Addresses  The A14 is a column LSB address and is controlled internally by SF signal.                                                                                 |

| CE        | Chip Enable Input            | The falling edge of $\overline{\text{CE}}$ latches the A0 $^{\circ}$ A14 and CS. The read data is retained in Read Latch (RL), even if the $\overline{\text{CE}}$ goes high. |

| CS        | Chip Select Input            | The low CS forbid the memory cell access operation, but allows the refresh operation. ( $\overline{\text{CE}}$ ONLY REFRESH)                                                 |

| RS        | Read Strobe Input            | The $\overline{RS}$ controls the transfer operation to Output Shift Register from Read Latch (RL).                                                                           |

| SF        | Special Function             | The SF controls the column LSB Al4 internally.                                                                                                                               |

| ws        | Write Strobe Input           | The $\overline{\text{WS}}$ controls the transfer operation to Write Latch (WL) from Input Shift Register.                                                                    |

| WE        | Write Enable Input           | The $\overline{\text{WE}}$ controls the write operation into the memory cell.                                                                                                |

| ŌĒ        | Output Enable Input          | The $\overline{\text{OE}}$ enables the DO1 $^{\circ}$ DO4 output buffers.                                                                                                    |

| RFSH      | Refresh Control Input        | The RFSH controls the auto refresh operation.                                                                                                                                |

| soc       | Serial Output Clock<br>Input | The SOC is a shift clock input to Output Shift Register.                                                                                                                     |

| SIC       | Serial Input Clock<br>Input  | The SIC is a shift clock input to Input Shift Register.                                                                                                                      |

| DO1 ∿ DO4 | Data Outputs                 | Serial Output Terminals.                                                                                                                                                     |

| DI1 ~ DI4 | Data Inputs                  | Serial Input Terminals.                                                                                                                                                      |

## ABSOLUTE MAXIMUM RATINGS (Note : 1)

| SYMBOL                            | ITEM                         | RATING    | UNIT   | NOTE |

|-----------------------------------|------------------------------|-----------|--------|------|

| V <sub>IN</sub> ·V <sub>OUT</sub> | Input • Output Voltage       | -1 ∿ 7    | v      | 2    |

| $v_{CC}$                          | Power Supply Voltage         | -1 ∿ 7    | V      | 2    |

| Topr                              | Operating Temperature        | 0 ∿ 70    | °C     |      |

| T <sub>stg</sub>                  | Storage Temperature          | -55 ∿ 150 | °C     |      |

| T <sub>solder</sub>               | Soldering Temperature • Time | 260 · 10  | °C•sec |      |

| $P_{D}$                           | Power Dissipation            | 1         | W      |      |

| IOUT                              | Short Circuit Output Current | 50        | mA     |      |

#### RECOMMENDED DC OPERATING CONDITIONS (Ta=0 ~ 70°C)

| SYMBOL   | PARAMETER            | MIN. | TYP. | MAX. | UNIT | NOTE |

|----------|----------------------|------|------|------|------|------|

| VCC      | Power Supply Voltage | 4.5  | 5.0  | 5.5  | V    | 2    |

| $v_{IH}$ | Input High Voltage   | 2.4  | -    | 6.5  | V    | .2   |

| VIL      | Input Low Voltage    | -1.0 | -    | 0.8  | V    | 2    |

DC ELECTRICAL CHARACTERISTICS (VCC=5V±10%, Ta=0 \(^2\) 70°C)

| SYMBOL              | PARAMETER                                                                                                            | MIN. | (10)<br>TYP. | MAX. | UNIT | NOTE |

|---------------------|----------------------------------------------------------------------------------------------------------------------|------|--------------|------|------|------|

| I <sub>CC1</sub>    | OPERATING CURRENT (CE, SIC, SOC Cycling: t <sub>C</sub> , t <sub>SIC</sub> , t <sub>SOC</sub> =min.)                 | _    | 65           | 100  | mA   | 3,4  |

| I <sub>CC2</sub>    | STANDBY CURRENT (CE-OE=V <sub>IL</sub> , SIC=SOC=V <sub>IL</sub> )                                                   | -    | 3            | 20   | mA   |      |

| I <sub>CC3</sub>    | REFRESH CURRENT (RFSH Cycling: tFC=tFC min.)                                                                         | -    | 50           | 100  | mA   | 3    |

| I <sub>I1</sub> (L) | INPUT LEAKAGE CURRENT (Except for SF Pin) (0V $\leq$ V <sub>IN</sub> $\leq$ 6.5V, All other pins not under test=0V). | -10  | -            | 10   | μA   |      |

| <sup>I</sup> 12(L)  | INPUT LEAKAGE CURRENT (SF Pin ONLY) (0V $\leq$ V <sub>IN</sub> $\leq$ 6.5V, All other pins not under test=0V)        | -50  | _            | 50   | μA   |      |

| <sup>I</sup> O(L)   | OUTPUT LEAKAGE CURRENT (OV $\leq$ VOUT $\leq$ VCC, Output is disabled)                                               | -10  | -            | 10   | μА   |      |

| v <sub>OH</sub>     | OUTPUT HIGH LEVEL VOLTAGE (IOUT=-2mA)                                                                                | 2.4  | -            | -    | V    |      |

| v <sub>OL</sub>     | OUTPUT LOW LEVEL VOLTAGE<br>(I <sub>OUT</sub> =2mA)                                                                  | -    | -            | 0.4  | v    |      |

CAPACITANCE (VCC=5V $\pm$ 10%, f=1MHz, Ta=0 $\sim$ 70°C)

| SYMBOL          | PARAMETER                                                      | MIN. | MAX. | UNIT | NOTE |

|-----------------|----------------------------------------------------------------|------|------|------|------|

| C <sub>I1</sub> | Input Capacitance (AO ^ A14)                                   | _    | 7    | pF   |      |

| C <sub>12</sub> | Input Capacitance (CE, CS, RS, WS, WE, OE, SF, RFSH, SIC, SOC) | _    | 7    | pF   |      |

| C <sub>13</sub> | Input Capacitance (DI1 ∿ DI4)                                  | _    | 7    | pF   |      |

| co              | Output Capacitance (DO1 ∿ DO4)                                 | _    | 9    | pF   |      |

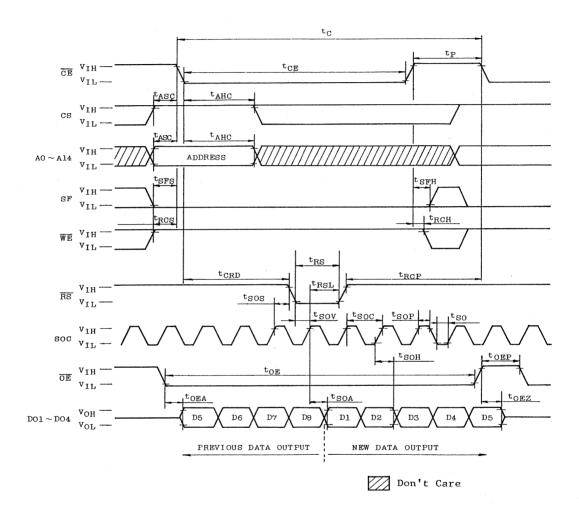

AC ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS ( $V_{CC}$ =5 $V\pm10\%$ , Ta=0  $\sim$  70°C) (Note: 5, 6, 7)

| SYMBOL           | PARAMETER                                                               | MIN. | MAX.  | UNIT | NOTE |

|------------------|-------------------------------------------------------------------------|------|-------|------|------|

| t <sub>C</sub>   | Read, Write Cycle Time                                                  | 190  |       | ns   |      |

| t <sub>RMW</sub> | Read-Modify-Write Cycle Time (=8x t <sub>SOC</sub> , t <sub>SIC</sub> ) | 240  |       | ns   |      |

| tRRW             | Read-Read-Write Cycle Time (=16x t <sub>SOC</sub> )                     | 480  |       | ns   |      |

| t <sub>CE</sub>  | CE Pulse Width                                                          | 100  | 2,000 | ns   |      |

| t <sub>P</sub>   | CE Precharge Time                                                       | 80   |       | ns   |      |

| tasc             | Address, CS Set-up Time                                                 | 0    |       | ns   |      |

| tAHC             | Address, CS Hold Time                                                   | 50   |       | ns   | 2.53 |

| tsoc             | Serial Output Cycle Time                                                | 30   |       | ns   |      |

| tso              | SOC Low Pulse Width                                                     | 10   |       | ns   |      |

| tsop             | SOC High Pulse Width                                                    | 10   |       | ns   |      |

| tsoA             | SOC Access Time                                                         |      | 20    | ns   | 8    |

| tsoH             | SOC Output Data Hold Time                                               | 5    |       | ns   |      |

| tsic             | Serial Input Cycle Time                                                 | 30   |       | ns   |      |

| t <sub>SI</sub>  | SIC Low Pulse Width                                                     | 10   |       | ns   |      |

| tSIP             | SIC High Pulse Width                                                    | 10   |       | ns   |      |

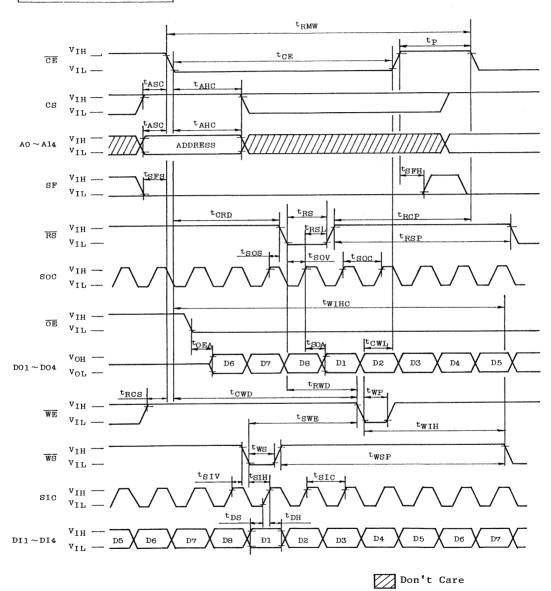

| t <sub>RCS</sub> | Read Command Set-up Time                                                | 0    |       | ns   |      |

| t <sub>RCH</sub> | Read Command Hold Time                                                  | 0    |       | ns   |      |

| <sup>t</sup> CRD | CE-RS Delay Time                                                        | 85   |       | ns   |      |

| t <sub>RS</sub>  | RS Pulse Width                                                          | 20   |       | ns   |      |

| tRCP             | RS-CE Precharge Time                                                    | 0    |       | ns   |      |

| t <sub>RSP</sub> | RS Precharge Time                                                       | 30   |       | ns   |      |

| tsos             | SOC-RS Set-up Time                                                      | 0    |       | ns   |      |

| tsov             | SOC-RS Hold Time                                                        | 15   |       | ns   |      |

| t <sub>RSL</sub> | SIC-RS Lead Time                                                        | 0    |       | ńs   |      |

| t <sub>OE</sub>  | OE Pulse Width                                                          | 30   |       | ns   |      |

| t <sub>OEP</sub> | OE Precharge Time                                                       | 30   |       | ns   |      |

| t <sub>OEA</sub> | $\overline{	ext{OE}}$ Access Time                                       |      | 25    | ns   | 8    |

| t <sub>OEZ</sub> | OE Output Buffer Turn-off Delay Time                                    | 0    | 30    | ns   | 9    |

| t <sub>RWD</sub> | RS-WE Delay Time                                                        | 0    |       | ns   |      |

| tCWD             | CE-WE Delay Time (Read-Modify-Write Cycle)                              | 90   |       | ns   |      |

| t <sub>WHC</sub> | WE Hold Time                                                            | 70   |       | ns   |      |

| t <sub>WP</sub>  | WE Pulse Width                                                          | 30   |       | ns   |      |

| tCWL             | WE-CE Lead Time                                                         | 40   |       | ns   |      |

# TC521000P/J

#### (Continued)

| SYMBOL           | PARAMETER                                                                  | MIN. | MAX.  | UNIT | NOTE |

|------------------|----------------------------------------------------------------------------|------|-------|------|------|

| t <sub>SWE</sub> | WS-WE Set-up Time                                                          | 20   |       | ns   |      |

| tws              | WS Pulse Width                                                             | 20   |       | ns   |      |

| twsp             | WS Precharge Time                                                          | 30   |       | ns   |      |

| tWIH             | $\overline{	extsf{WS}}$ Inhibit Time referenced to $\overline{	extsf{WE}}$ | 50   |       | ns   |      |

| twihc            | $\overline{	ext{WS}}$ Inhibit Time referenced to $\overline{	ext{CE}}$     | 100  |       | ns   |      |

| tsiv             | SIC-WS Set-up Time                                                         | 5    |       | ns   |      |

| tsiH             | SIC-WS Hold Time                                                           | 10   |       | ns   |      |

| t <sub>DS</sub>  | Data Input Set-up Time                                                     | 5    |       | ns   |      |

| t <sub>DH</sub>  | Data Input Hold Time                                                       | 5    |       | ns   |      |

| tSFS             | SF-CE Set-up Time                                                          | 0    |       | ns   |      |

| t <sub>SFH</sub> | SF-CE Hold Time                                                            | 0    |       | ns   |      |

| t <sub>CSL</sub> | SF-CE Lead Time (Read-Read-Write Cycle)                                    | 50   |       | ns   |      |

| tssH             | SOC-SF Hold Time (Read-Read-Write Cycle)                                   | 20   |       | ns   |      |

| tT               | Transition Time (Rise and Fall)                                            | 3    | 50    | ns   | 7    |

| t <sub>REF</sub> | Refresh Period                                                             |      | 8     | ms   |      |

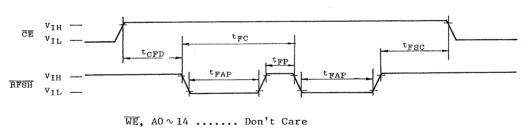

| t <sub>FC</sub>  | Refresh Cycle Time                                                         | 190  |       | ns   |      |

| tCFD             | CE Precharge-RFSH Delay Time                                               | 80   |       | ns   |      |

| t <sub>FAP</sub> | RFSH Pulse Width                                                           | 100  | 2,000 | ns   |      |

| t <sub>FP</sub>  | RFSH Precharge Time                                                        | 80   |       | ns   |      |

| t <sub>FSC</sub> | RFSH Precharge-CE Delay Time                                               | 80   |       | ns   |      |

#### Notes

- (1) Stress greater than those listed under "Absolute Maximum Ratings" may cause Permanent damage to the device.

- (2) All voltages are referenced to VSS.

- (3)  $I_{\rm CC1}$  and  $I_{\rm CC2}$  depend on cycle time. These values are specified at the condition of minimum cycle time.

- (4) ICC1 depends on output loading. Specified value is obtained with the output open.

- (5) An initial pause of 200 $\mu s$  is required after power up followed by 8  $\overline{\text{CE}}$  cycles before proper device operation is achieved. In case of using auto refresh, a minimum of 8  $\overline{\text{RFSH}}$  cycle are required.

- (6) AC measurements assume t<sub>T</sub>=5ns.

- (7)  $V_{\rm IH}(\text{min.})$  and  $V_{\rm IL}(\text{max.})$  are reference levels for measuring timing of input signals. Also transition times are measured between V<sub>IH</sub> and V<sub>II.</sub>

- Also transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

(8) Output timings are measured with a load equivalent to 2 TTL load and 30pF.

DOUT comparate level: V<sub>OH</sub>/V<sub>OL</sub>=2.0V/0.8V

- (9)  $t_{OEZ}(max.)$  defines the time at which the output achieve the open state.

- (10) Typical values are at  $Ta=25^{\circ}C$  and VCC=5.0V.

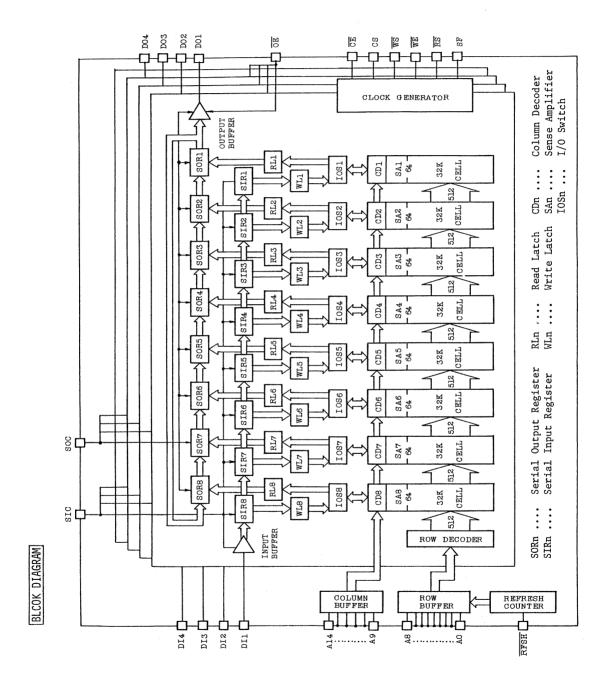

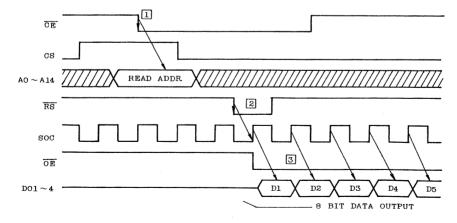

#### READ/SERIAL READ CYCLE

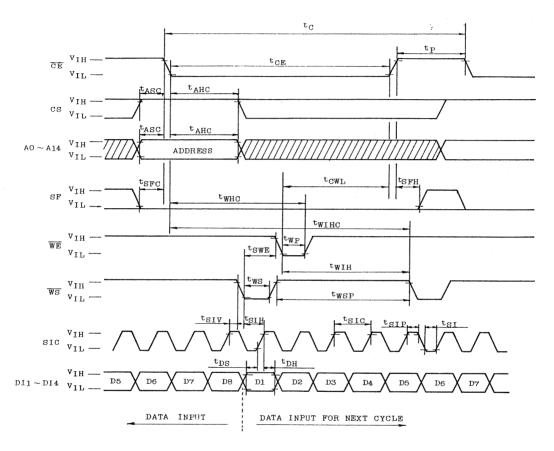

## WRITE/SERIAL WRITE CYCLE

Don't Care

#### READ MODIFY WRITE CYCLE

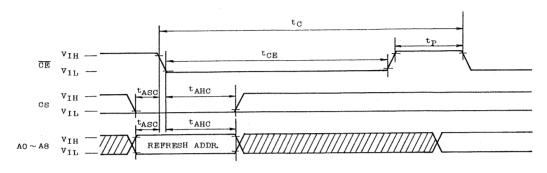

#### CE ONLY REFRESH

$\overline{\text{WE}}$ , A9  $\sim$  14 ..... Don't Care

#### RFSH AUTO REFRESH

Don't Care

#### OPERATION INFORMATION

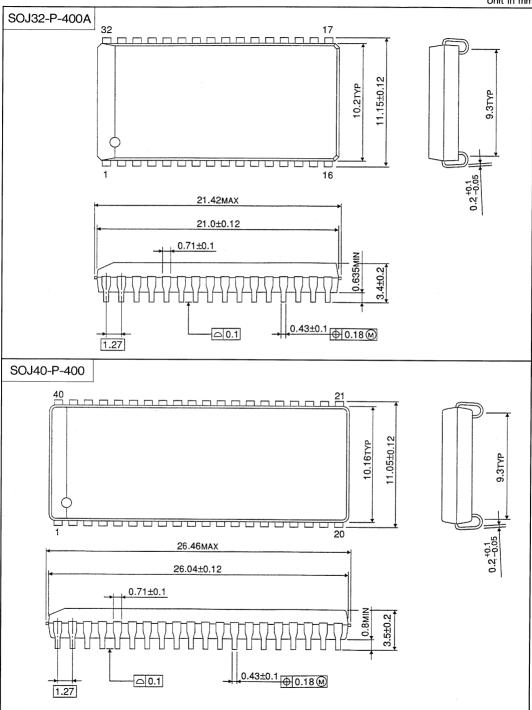

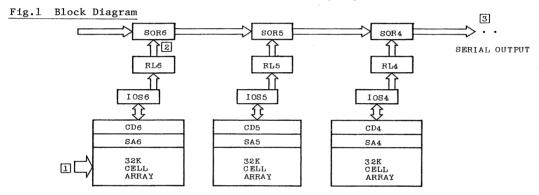

- (1) READ/SERIAL READ CYCLE

- i) SERIAL READ CYCLE (Refer to Fig. 1, 2)

- $\boxed{1}$  The read address is latched at the falling edge of  $\overline{\text{CE}}$ . The 8 bit data read out are transferred to and latched into the read latch (RL).

- $\boxed{2}$  The data latched at the RL are transferred to serial output register (SOR) at the first rising edge of SOC after the  $\overline{\text{RS}}$  goes low.

- $\boxed{3}$  The 8 bit data transferred to the SOR are shifted and output sequentially synchronized with SOC from the first rising edge of SOC after the  $\overline{\text{RS}}$  falls.

Fig.2 Timing Diagram

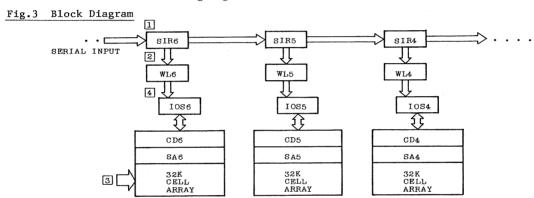

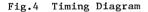

- (2) WRITE/SERIAL WRITE CYCLE (Refer to Fig. 3, 4)

- 1 The 8 bit input data are latched into the 8 bit serial input register (SIR) sequentially synchronized with SIC.

- $\fbox{2}$  The 8 bit input data latched into the SIR are transferred to the write latch (WL) at the falling edge of  $\overline{\text{WS}}$ .

- $\fbox{3}$  The write address is latched at the falling edge of  $\fbox{CE}$ , same as read operation. Then the data stored in selected address to be written are read out and latched into the RL independent of this write operation, so the read data latched there can be read out through SOR by using  $\fbox{RS}$  and SOC (Read-Modify-Write).

- The 8 bit input data latched into the WL are written into the selected address location at the falling edge of  $\overline{\text{WE}}$ .

# TC521000P/J

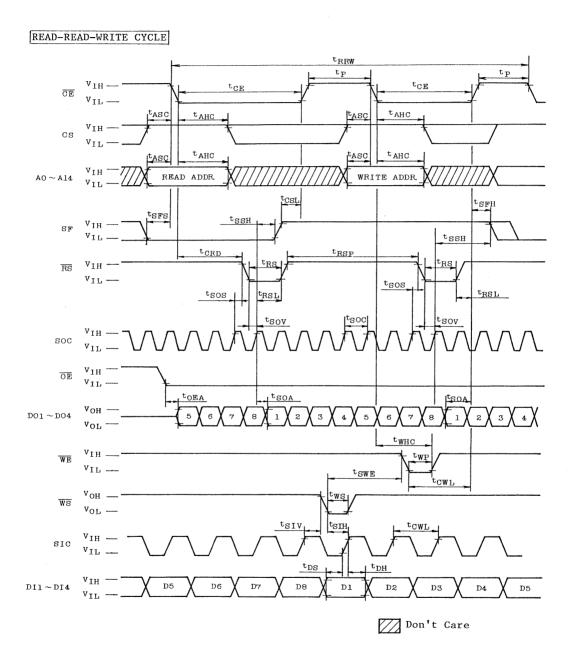

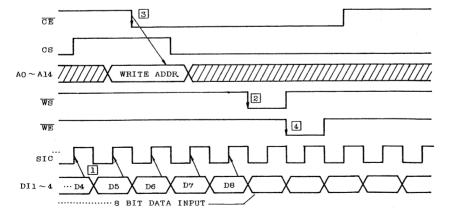

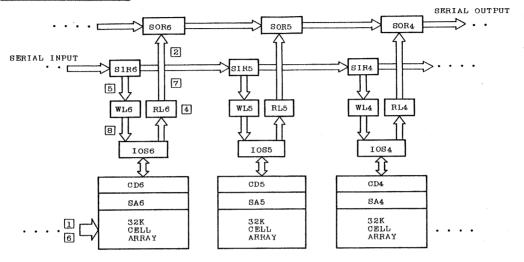

- (4) READ-WRITE CYCLE (Special operation) (Refer to Fig. 5, 6)

By using SF signal, three operations the read operation for consecutive two address (16 bit data output) and write operation into the different address from read (8 bit data input) can be performed asynchronously in two CE cycles (480ns). In this operation, the read start address must be even. This operation capability allows the field double scan in order to improve the picture quality in TV applications.

- 1 The read address (even) is latched at the falling edge of  $\overline{\text{CE}}$  under the condition of SF=low. Then the 8 bit read out data are transferred to and latched into the RL.

- $\boxed{2}$  The 8 bit data latched into the RL are transferred to SOR by the  $\overline{\text{RS}}$ , and then the data latched into the SOR are shifted and output from the first rising edge of SOC after the  $\overline{\text{RS}}$  falls.

- 3 Then when SF goes high, the LSB bit (A14) of coulumn addresses is changed to "1" from "0" automatically, and the data in the next column address are transferred to and latched into the RL.

- When the  $\overline{\text{CE}}$  goes high, only memory cell array its peripheral area except for the latch and serial registers are placed in a precharge state. Then the data latched into the RL and SOR are maintained there, so the  $\overline{\text{WS}}$  and  $\overline{\text{RS}}$  can be input.

- $\overline{5}$  On the other hand, the 8 bit input data are latched into the SIR sequentially synchronized with the SIC and then transferred to and latched into the WL by the  $\overline{WS}$ .

- The write address is latched at the falling edge of  $\overline{\text{CE}}$ , and then the data stored in the selected address is read out, but the data already latched into the RL are protected and retained there because of maintaining the SF "high".

- The 8 bit data latched into the RL (in  $\boxed{3}$ ) are transferred to and latched into the SOR by the  $\overline{\text{RS}}$ .

- [8] The 8 bit data latched into the WL (in  $\boxed{5}$ ) are written into the selected cell locations by the  $\overline{\text{WE}}$ .

Fig.5 Block Diagram

Fig.6 Timing Diagram

# TC521000P/J·

#### (5) REFRESH

The TC521000P/J's refresh period is 8ms/512 cycles. Two types of refresh operation -  $\overline{\text{CE}}$  only refresh and  $\overline{\text{RFSH}}$  auto refresh - are allowed.

#### 5-1: $\overline{CE}$ only refresh

The refresh is accomplished by performing a  $\overline{\text{CE}}$  cycle at each of the 512 low address (A0  $^{\circ}$  A8) within each 8ms time interval.

#### 5-2: RFSH auto refresh

The  $\overline{\text{RFSH}}$  auto refreshis available on the TC521000P/J. When the  $\overline{\text{RFSH}}$  goes low under the condition of  $\overline{\text{CE}}$ =high, on chip refresh control clock generator and refresh address counters are enabled. Then, the refresh is accomplished by applying 512 clocks to the  $\overline{\text{RFSH}}$  input within 8ms time interval.

# DATA BOOK **TOSHIBA** 1991 MOS MEMORY (VRAM, SRAM)

# INTRODUCTION

We continually venture at the leading edge of technology so that we may develop and offer to you a diverse array of semiconductor memory products which may be used in many commercial and industrial applications. At this time, we offer three data books; "MOS-Memory Dynamic RAM and Module", "MOS-Memory Video RAM and Static RAM" and "MOS-Memory ROM".

Particularly, this data book is "MOS-Memory Video RAM and Static RAM" edition.

These data books represent our current culminations of electrical characteristics, timing waveforms and package data for our line of semiconductor memory products.

We hope this information will be very useful for you.

Nov. 1991

TOSHIBA CORPORATION

Semiconductor Group